Informatik am Gymnasium Trittau/Digitale Informationsverarbeitung/4-Bit-Addierer: Unterschied zwischen den Versionen

GT039 (Diskussion | Beiträge) (Text zum 4-Bit-Addierers hinzugefügt) Markierung: Quelltext-Bearbeitung 2017 |

GT039 (Diskussion | Beiträge) (Foto hinzugefügt zum 4-Bit-Addierer) |

||

| Zeile 1: | Zeile 1: | ||

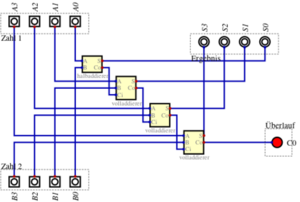

[[Datei:470px-Digital 4-Bit Addierer.svg.png|mini|Beispiel eines 4-Bit-Addierers]] | |||

Der 4-Bit-Addierer kann zwei Binärzahlen mit vier Stellen addieren. Er setzt sich zusammen aus drei Volladdierern und einem Halbaddierer. Diese sind so angeordnet, dass der Halbaddierer zuerst die ersten zwei Stellen Stellen addiert. In einer schriftlichen Addition wären es die hintersten Stelle der beiden Summanden. | Der 4-Bit-Addierer kann zwei Binärzahlen mit vier Stellen addieren. Er setzt sich zusammen aus drei Volladdierern und einem Halbaddierer. Diese sind so angeordnet, dass der Halbaddierer zuerst die ersten zwei Stellen Stellen addiert. In einer schriftlichen Addition wären es die hintersten Stelle der beiden Summanden. | ||

Aktuelle Version vom 14. Dezember 2022, 07:04 Uhr

Der 4-Bit-Addierer kann zwei Binärzahlen mit vier Stellen addieren. Er setzt sich zusammen aus drei Volladdierern und einem Halbaddierer. Diese sind so angeordnet, dass der Halbaddierer zuerst die ersten zwei Stellen Stellen addiert. In einer schriftlichen Addition wären es die hintersten Stelle der beiden Summanden.

Der Übertrag dieser Addition wird als drittes Eingangssignal in den Volladdierer geleitet, also ein Ausgang als Ausgangssignal und das andere als Übertrag. Die anderen beiden Signale sind die nächsten Ziffern der Zahlen. Bei einer schriftlichen Addition wäre es die zweite Stelle der Summanden.

Dieser Vorgang wir wiederholt (erste beiden Eingänge die neuen Ziffern und dritter Eingang der Übertrag des vorherigen Addierers), bis alle Ziffern der Binärzahlen als Eingangssignal verarbeitet sind. Der letzte Übertrag wird, anders als alle anderen, nicht erneut verrechnet, sondern ist ein einfaches Ausgangssignal.